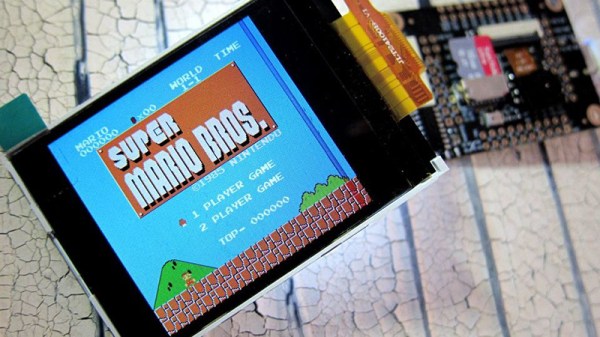

RISC architecture might change the world, but it runs an NES emulator right now. That’s thanks to MaixPy, the new MicroPython for the K210, the recently released RISC-V microcontroller that’s making waves in the community. [Robot Zero One] has the tutorial and [Other Dave] of EEVBlog has a video of the thing in action.

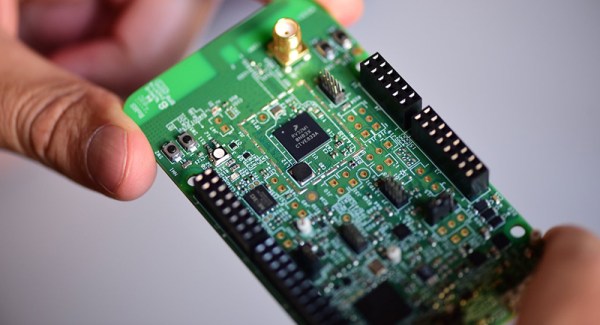

The Sipeed K210 came to the English-speaking world in the form of a weird pre-order thing on Taobao last October promising a dual-core RISC-V CPU for just a few bucks. Seeed, the same people who brought the ESP8266 into mass distribution quickly latched on and started selling modules last February. Now, Seeed is looking at a Raspberry Pi hat using a Sipeed module, and the future for RISC-V microcontrollers is looking great. Now someone just needs to write some software. That’s exactly what the engineers at Sipeed did, and somewhere in one of the released binaries there’s an NES emulator.

The parallel to the question of if something can run Doom is if something can run an NES emulator, so with the release of MicroPython support for the K210, the obvious thing to do is to release an NES emulator. The hardware required is a Maix M1w Dock, available from Seeed and Banggood.

The new support for MicroPython is great, and an NES emulator is amazing, but this should really come as no surprise. From our first hands on with the first Open Source microcontroller two years ago, RISC-V was obviously faster. Now it’s cheap, and we can’t wait to see what’ll come next.