After the Norman invasion of England, William the Conqueror ordered a great reckoning of all the lands and assets owned. Tax assessors went out into the country, counted sheep and chickens, and compiled everything into one great tome. This was the Domesday Book, an accounting of everything owned in England nearly 1000 years ago. It is a vital source for historians and economists, and one of the most important texts of the Middle Ages.

In the early 1980s, the BBC set upon a new Domesday Project. Over one million people took part in compiling writings on history, geography, and social issues. Maps were cataloged, and census data recorded. All of this was printed on a LaserDisk, meant to be played on an Acorn BBC Master. Now, 30 years on, hardly anyone can read the BBC Domesday Project. Let that be a lesson, kids: follow [Jason Scott] on Twitter.

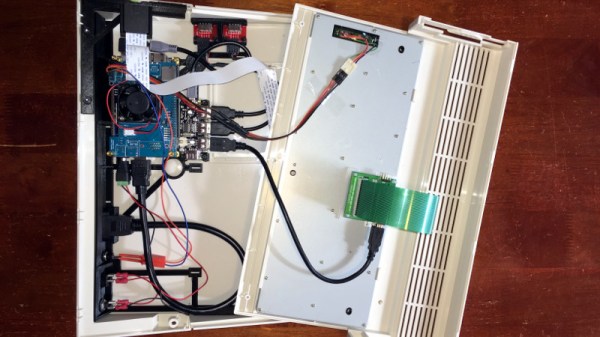

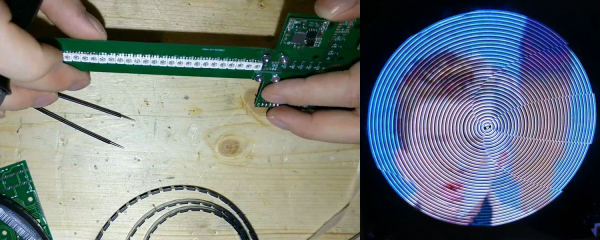

Even though Acorn computers and SCSI LaserDisks and coprocessors are dying, that doesn’t mean the modern Domesday Disk is lost to the sands of time. This project aims to duplicate the Domesday Disk, and in the process provide a means to archive all LaserDisks. It’s a capture card for LaserDisks, and it also means we can finally make a good rip of the un-specalized Star Wars.

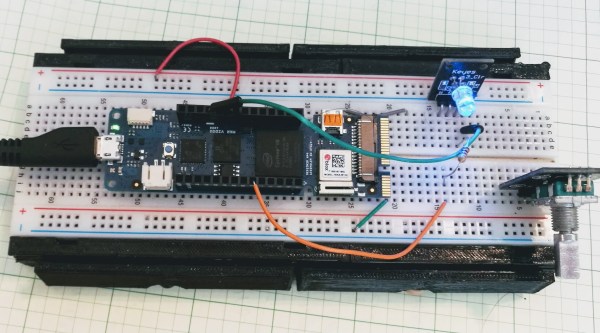

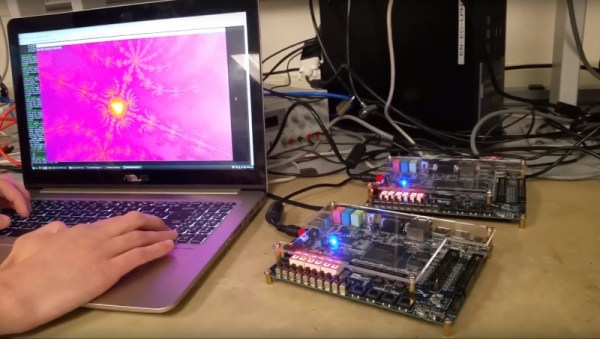

The Domesday Duplicator is a shield that plugs into an Altera DE-0 Nano FPGA board and a Cypress FX3 USB board. The Duplicator itself serves as an analog capture card complete with an RF amplifier and a 40 MSPS ADC — fast enough for any analog video signal. With the 50 Ohm input, it will work with most LaserDisk players, ultimately preserving this incredible historical archive from the early 80s.