Every hacker has an assortment of USB to TTL-serial adapters kicking around in their lab, and we have all been annoyed that each one has a different pinout. You layout a PCB or breadboard for the Sparkfun flavor (GND, CTS, VCC, TXD, RXD, DTR), but when you begin troubleshooting all you can find is a CH340 board (GND, +5V, TXD, RXD, DTR, +3.3V). You have to jumper everything, and it becomes a mess. It wasn’t much better back in the days of RS-232 level signaling, either. While the pinouts were consistent, there were other headaches. Did the connection need a NULL modem adaptor? And if you were unlucky, you might need a DB-25 to DE-9 adaptor, and the really unlucky might need one or more gender changers. Surely there’s a better way.

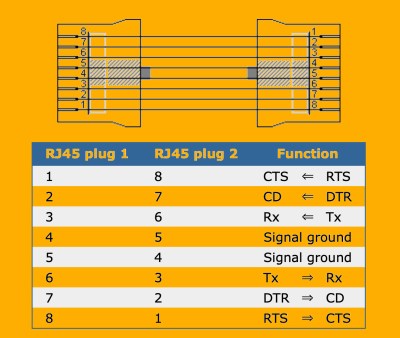

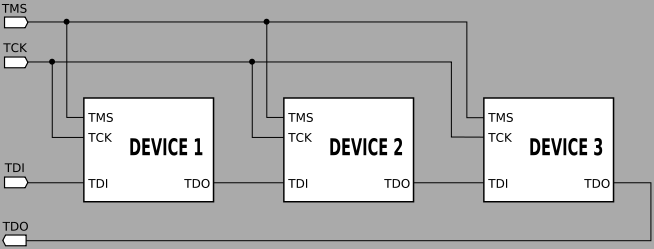

It turns out there was a better way, although it didn’t seem to have become as popular as one might expect. Back in 1987 [Dave Yost] formalized an interconnection scheme using RJ45 plugs and jacks while at Berkeley. The signals were arranged in a mirrored fashion so that each cable is always a crossover — just plug two cables back-to-back if you really need a straight thru connection.

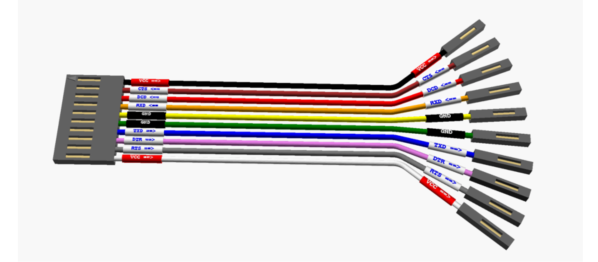

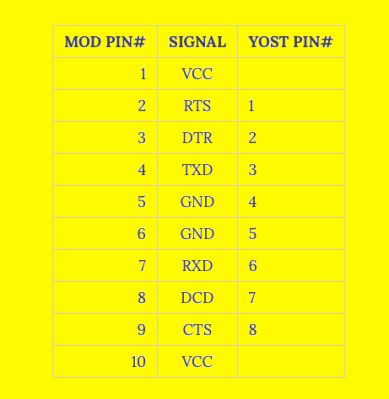

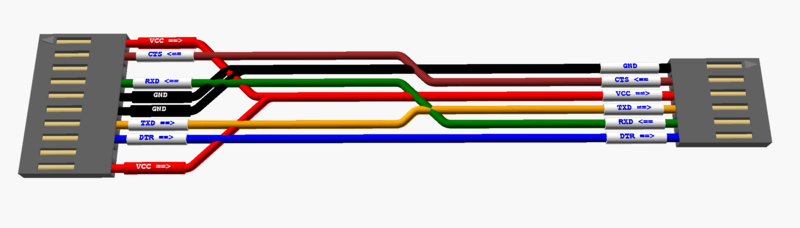

Even though he was dealing with RS-232 serial, nothing prevents us from using this scheme for logic level signaling. For example, consider the following 1×10 header pinout, where the original 8-pins are expanded to 10 to allow for power:

This is an extreme example, and can obviously be shrunk depending on how much handshaking, if any, or power is desired. Such a pinout lets you switch between DCE and DTE by simply flipping the connector around. And if a Dupont-style header slips off too easily in your applications, you could always use an RJ connector. This still doesn’t solve the Tower of Babel pinout problem with the USB-TTL adaptors. But standardizing on a serial pinout such as this for your projects and making cables or kludging your TTL adaptors will make serial debugging less painful.

Back when he released this scheme in 1987, [Dave] pontificated:

“Maybe one day before the year 2,000, the world will have a new, simple, high-speed, flow-controlled, standard type of connection for point-to-point applications currently using RS-232, with an adaptor available to talk to old, RS-232 equipment.”

Let us know your thoughts in the comments below.