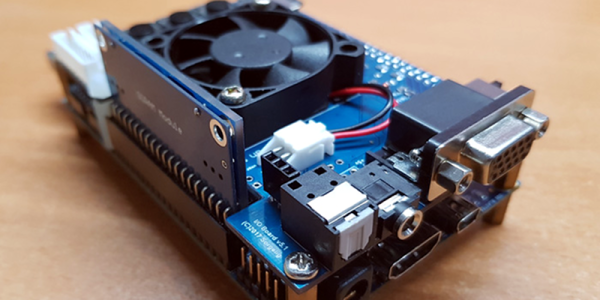

We like cheap FPGA boards. It isn’t just that we’re cheap — although that’s probably true, too — but cheap boards are a good way to get people started on FPGAs and we think more people should be using FPGAs more often. One inexpensive board is the Max-1000 from Trenz and Arrow. At $29, it is practically an impulse buy. [ZipCPU] did a great write up on his experience using the board. He found that some of it was good, some was bad, and some was just plain ugly. Still, for $30, it seems like this might be a nice board for some applications or for getting started.

Billed an IoT Maker Board, the tiny board sports a Intel (formerly Altera) MAX10 device with 8,000 logic elements, a USB programming interface onboard, 8 MB of SDRAM, and both PMOD and Arduino MKR headers. The MAX10 has an analog to digital conversion block (with an analog mux for up to nine channels) and the ability to host a 32-bit soft controller onboard, too.