Today’s CPUs are so advanced that they might as well be indistinguishable from magic, right? Wrong! Fundamentally, modern CPUs can be understood logically like any other technology, it’s just that they’re very fast, very small, and very complex, which makes it hard to get to grips with their inner workings. We’ve come a long way from the dawn of the home computer in the 80s, but what if there was something even simpler again, built in such a way as to be easily understandable? Enter the DDL-4-CPU, courtesy of [Dave’s Dev Lab].

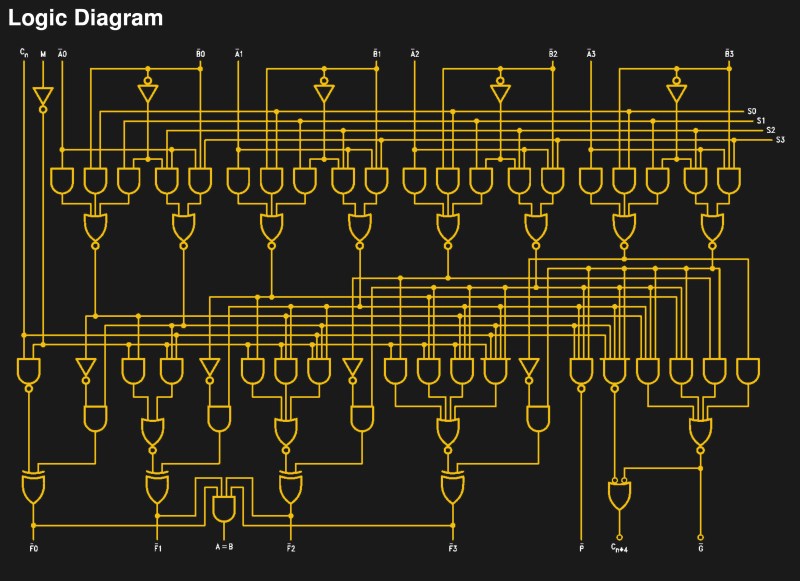

The DDL-4 is a project to build a modular 4-bit CPU using bitslice methods. This is where computations are broken down into simple operations with two-bit inputs, which are executed with basic logic gates like NOR and XOR. This is great for building a CPU from individual parts, as logic chips are readily available and their operation is readily understood. That’s what’s used here – good old 74-series logic, which you can find just about anywhere!

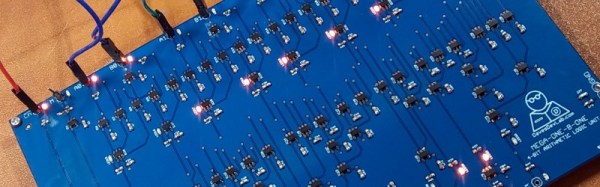

The build consists of a series of modules, each on its own colourful PCB and labeled on the silkscreen. These modules can then be configured and plugged together with edge connectors to build the CPU. The work builds upon [Dave]’s earlier work on the Mega-One-8-One, a recreation of the 74181 Arithmetic Logic Unit for educational purposes.

If you’re learning about computing in a bare-metal sense, projects like these that create CPUs from the ground up are a great way to get to grips with the basic concepts of computation. Once you’ve tried this, you could always graduate to building a 6502 in Minecraft.

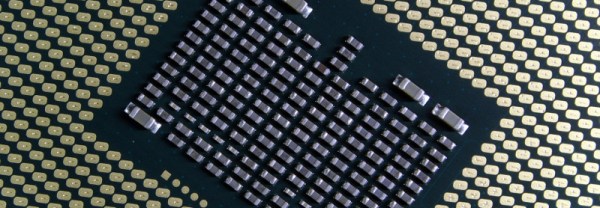

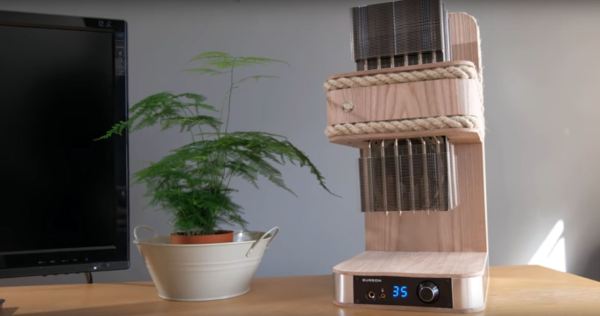

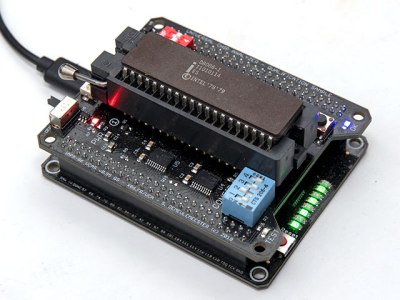

So, how does it actually test? Synthesized inside the FPGA is everything the CPU needs from the motherboard to make it tick, including ROM, RAM, bus controllers, clock generation and interrupt handling. Many testing frequencies are supported (which is helpful for spotting fakes), and if connected to a computer via USB, the UCA can check power consumption, and even benchmark the chip. We can’t begin to detail the amount of thought that’s gone into the design here, from auto-detecting data bus width to the sheer amount of models supported, but you can read more technical details

So, how does it actually test? Synthesized inside the FPGA is everything the CPU needs from the motherboard to make it tick, including ROM, RAM, bus controllers, clock generation and interrupt handling. Many testing frequencies are supported (which is helpful for spotting fakes), and if connected to a computer via USB, the UCA can check power consumption, and even benchmark the chip. We can’t begin to detail the amount of thought that’s gone into the design here, from auto-detecting data bus width to the sheer amount of models supported, but you can read more technical details