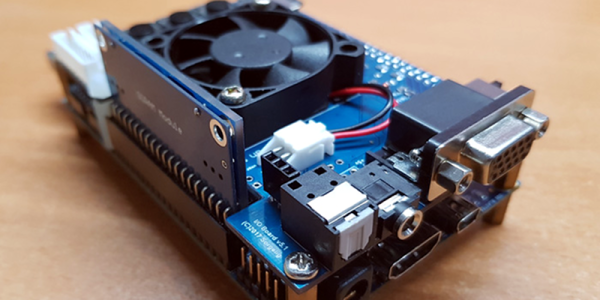

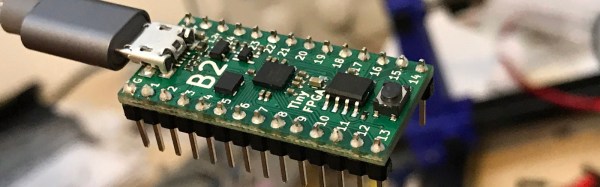

How would you sell a computer to a potential buyer? Fast? Reliable? Great graphics and sound? In 1956, you might point out that it was somewhat smaller than a desk. After all, in those days what people thought of as computers were giant behemoths. Thanks to modern FPGAs, you can now have a replica of a 1956 computer — the LGP-30 — that is significantly smaller than a desk. The LittleGP-30 is the brainchild of [Jürgen Müller].

The original also weighed about 740 pounds, or a shade under 336 kg, so the FPGA version wins on mass, as well. The LGP-30 owed its relative svelte footprint to the fact that it only used 113 tubes and of those, only 24 tubes were in the CPU. This was possible, because, like many early computers, the CPU worked on one bit at a time. While a modern computer will add a word all at once, this computer — even the FPGA version — add each operand one bit at a time.