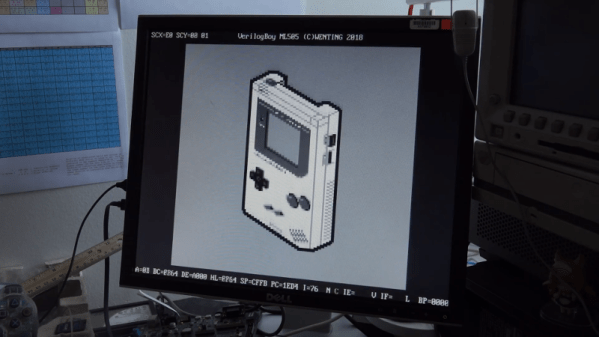

With the wide availability of Raspberry Pi hardware and pre-baked Linux distros with emulators ready to go, making a retro handheld is easier than ever. Emulation isn’t the only way to go about playing old games however. [Wenting Zhang] decided to instead recreate the Nintendo Game Boy in Verilog, and has documented the effort.

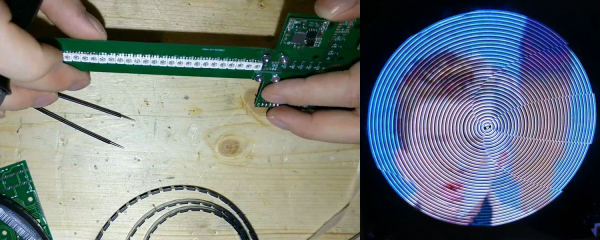

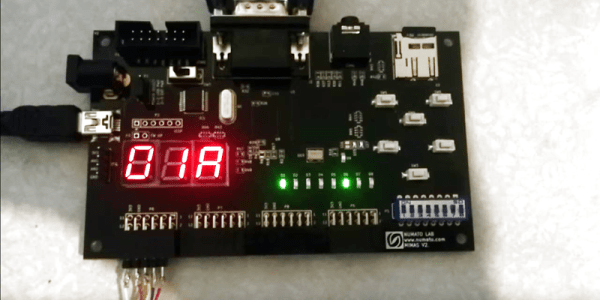

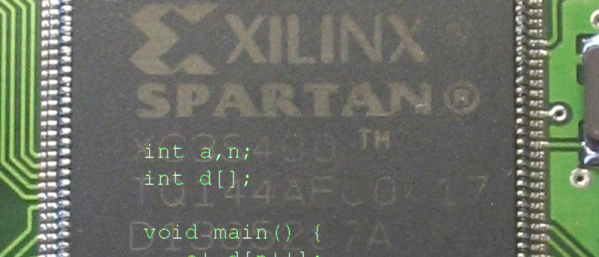

The project runs on a Spartan 6 FPGA. [Wenting] first developed the hardware to use a DualShock controller for input, and output video to a regular LCD monitor. However, work is now underway to produce a handheld VerilogBoy. This will feature a 320×320 LCD screen, with pixels being quadrupled from the original Game Boy 160×144 resolution, with some pixels to spare. [Wenting] is also looking at porting the code to some Pano Logic units, which we’ve discussed before. The thin clients pack FPGA hardware and lots of IO ports that make them perfect for such a project.

Code is available on Github for the curious tinkerers out there. While there are easier ways to play old handheld games, the amount of learning value of such a project should not be underestimated. We’ve seen FPGAs used for other Nintendo hijinx, too – like this NES cart that packs some serious muscle. Video after the break.