Everyone likes to play with high voltages, right?. Even though the danger of death goes up with every volt, it’s likely that a few readers will have at some time or other made fancy long sparks. You’re reading this so you lived to tell the tale, and we’d only ever counsel only doing so safely, but the point of this piece lies not in the volts themselves but in a touch of frustration at the voltage generators. There’s a circuit I see so often which annoys me every single time, so here if you don’t mind I’m going to deliver both a little rant and a look into flyback converters.

It’s Got Coils, so It’s A Transformer

How does a transformer work? An alternating current in a primary winding induces an opposite current in its secondary winding. The voltage out is equal to the turns ratio times the voltage in. Thus if you want to make a high voltage, it’s simply a case of finding a transformer with the right turns ratio, and applying the right AC to the input.

A handy choice for a high voltage transformer has been for years a TV line output transformer, also sometimes known as a flyback transformer. You could find these in CRT displays and TVs, and they consist of a square ferrite core with a big chunky high voltage overwinding for the CRT anode circuit and a load of lower voltage windings. TV designers were always out to save on parts costs, so they often had windings for all the voltage rails inside the set as well as the anode voltage, using the timebase as a crude switching power supply. Continue reading “A Pulse Of Annoyance About Oscillators, Followed By A Flyback Of A Rant”

In this article, let’s figure out places where you can use a logic analyzer, and places where you can’t. We’ll start with the first limitation of logic analyzers – capture speed. For instance, here’s a cool thing you can buy on Aliexpress – a wristband from TTGO that looks like a usual fitness tracker, but has an ESP32 in it, together with an IMU, an RTC, and an IPS screen! The seller also has an FFC-connectable devboard for programming this wristband over UART, plus vibromotor and heartrate sensor expansion modules.

In this article, let’s figure out places where you can use a logic analyzer, and places where you can’t. We’ll start with the first limitation of logic analyzers – capture speed. For instance, here’s a cool thing you can buy on Aliexpress – a wristband from TTGO that looks like a usual fitness tracker, but has an ESP32 in it, together with an IMU, an RTC, and an IPS screen! The seller also has an FFC-connectable devboard for programming this wristband over UART, plus vibromotor and heartrate sensor expansion modules.

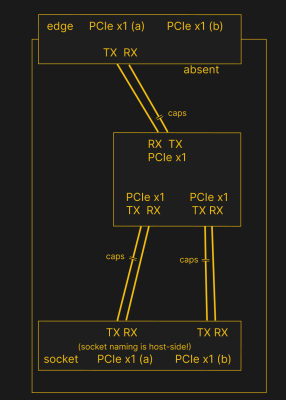

PCIe needs TX pairs connected to RX on another end, like UART – and this is non-negotiable. Connectors will use host-side naming, and vice-versa. As the diagram demonstrates, we connect the socket’s TX to chip’s RX and vice-versa; if we ever get confused, the laptop schematic is there to help us make things clear. To sum up, we only need to flip the names on the link coming to the PCIe switch, since the PCIe switch acts as a device on the card; the two links from the switch go to the E-key socket, and for that socket’s purposes, the PCIe switch acts as a host.

PCIe needs TX pairs connected to RX on another end, like UART – and this is non-negotiable. Connectors will use host-side naming, and vice-versa. As the diagram demonstrates, we connect the socket’s TX to chip’s RX and vice-versa; if we ever get confused, the laptop schematic is there to help us make things clear. To sum up, we only need to flip the names on the link coming to the PCIe switch, since the PCIe switch acts as a device on the card; the two links from the switch go to the E-key socket, and for that socket’s purposes, the PCIe switch acts as a host.