Last time, I showed you a simple PWM block and an open source UART core. This time, I’ll put these parts together to create a PC PWM output peripheral.

verilog93 Articles

A Modern 386 Development Board

Some readers out there probably have nostalgic feelings for their first 386 based PC, the beeps and hisses of the modem, and the classic sound of a floppy drive’s stepper motor. Perhaps that turbo button that we could never quite figure out.

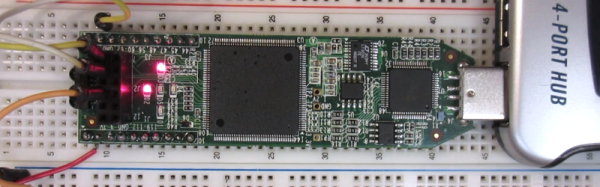

If you want the power of a 386 processor today, you’re in luck: [Pierre Surply] has developed a modern development board for the 80386SX CPU. This board is based on a 386 processor that comes in a LQFP package for “easy” soldering, and an Altera Cyclone IV FPGA.

To allow the CPU to run, the FPGA emulates the chipset you would usually find on a PC motherboard. The FPGA acts as both a bus controller and a memory controller for the CPU. On the board, there’s an SRAM chip and internal memory on the FPGA, which can be accessed through the 386’s bus access protocol.

The FPGA also provides debugging features. A supervisor application running on the FPGA gives debugging functionality via a FTDI USB to UART chip. This lets you control operation of the CPU from a PC for debugging purposes. The FPGA’s memory can be programmed through a JTAG interface.

The project is very well documented, and is a great read if you’re wondering how your old 386 actually worked. It can even be hand soldered, so the adventurous can grab the design files and give it a go. The francophones reading can also watch the talk in the video below.

Learn Flip Flops With (More) Simulation

In the previous installment, we talked about why flip flops are such an important part of digital design. We also looked at some latch circuits. This time, I want to look at some actual flip flops–that is circuit elements that hold their state based on some clock signal.

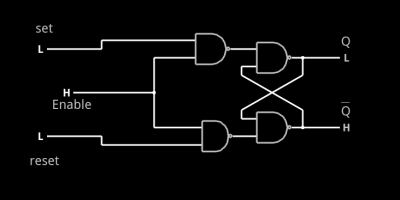

Just like last time, I want to look at sequential building blocks in three different ways: at the abstraction level, at the gate level, and then using Verilog and two online tools that you can also use to simulate the circuits. Remember the SR latch? It takes two inputs, one to set the Q output and the other to reset it. This unassuming building block is at the heart of many other logic circuits.

A common enhancement to the SR latch is to include an enable signal. This precludes the output from changing when the enable signal is not asserted. The implementation is simple. You only need to put an additional gate on each input so that the output of the gate can’t assert unless the other input (the enable) is asserted. The schematic appears on the right.

A common enhancement to the SR latch is to include an enable signal. This precludes the output from changing when the enable signal is not asserted. The implementation is simple. You only need to put an additional gate on each input so that the output of the gate can’t assert unless the other input (the enable) is asserted. The schematic appears on the right.

In the case of this simulation (or the Verilog equivalent), the SR inputs become active high because of the inversion in the input NAND gates. If the enable input is low, nothing will change. If it is high, then asserted inputs on the S or R inputs will cause the latch to set or reset. Don’t set both high at the same time when the enable is high (or, go ahead–it is a simulation, so you can’t burn anything up).(Note: If you can’t see the entire circuit or you see nothing in the circuit simulator, try selecting Edit | Centre Circuit from the main menu.)

Learn Flip Flops With Simulation

Digital design with combinatorial gates like AND, OR, and NOT gates is relatively straightforward. In particular, when you use these gates to form combinatorial logic, the outputs only depend on the inputs. The previous state of the outputs isn’t important in combinatorial logic. While this is simple, it also prevents you from building things like state machines, counters, and even CPUs.

Circuits that use their own outputs as inputs are known as sequential circuits. It is true that at the fundamental level, sequential circuits use conventional logic gates. However, you usually won’t deal with them as gates, but will deal with abstractions like latches, flip flops, and even higher level constructs. Learning about these higher level constructs will allow you to make more advanced digital designs that are robust. In fact, if you are using an FPGA, building blocks like flip flops are essential since a large portion of the chip will be made up of some kind of flip flop.

Learning Verilog For FPGAs: Hardware At Last!

Getting into FPGA design isn’t a monolithic experience. You have to figure out a toolchain, learn how to think in hardware during the design, and translate that into working Verliog. The end goal is getting your work onto an actual piece of hardware, and that’s what this post is all about.

In the previous pair of installments in this series, you built a simple Verilog demonstration consisting of an adder and a few flip flop-based circuits. The simulations work, so now it is time to put the design into a real FPGA and see if it works in the real world. The FPGA board we’ll use is the Lattice iCEstick, an inexpensive ($22) board that fits into a USB socket.

Like most vendors, Lattice lets you download free tools that will work with the iCEstick. I had planned to use them. I didn’t. If you don’t want to hear me rant about the tools, feel free to skip down to the next heading.

Continue reading “Learning Verilog For FPGAs: Hardware At Last!”

Learning Verilog For FPGAs: Flip Flops

Last time I talked about how to create an adder in Verilog with an eye to putting it into a Lattice iCEstick board. The adder is a combinatorial circuit and didn’t use a clock. This time, we’ll finish the demo design and add two clocked elements: a latch that remembers if the adder has ever generated a carry and also some counters to divide the 12 MHz clock down to a half-second pulse to blink some of the onboard LEDs.

Why Clocks?

Clocks are an important part of practical digital design. Suppose you have a two input AND gate. Then imagine both inputs go from zero to one, which should take the output from zero to one, also. On paper, that seems reasonable, but in real life, the two signals might not arrive at the same time. So there’s some small period of time where the output is “wrong.” For a single gate, this probably isn’t a big deal since the delay is probably minuscule. But the errors will add up and in a more complex circuit it would be easy to get glitches while the inputs to combinatorial gates change with different delays.

Learning Verilog For FPGAs: The Tools And Building An Adder

Over the last year we’ve had several posts about the Lattice Semiconductor iCEstick which is shown below. The board looks like an overgrown USB stick with no case, but it is really an FPGA development board. The specs are modest and there is a limited amount of I/O, but the price (about $22, depending on where you shop) is right. I’ve wanted to do a Verilog walk through video series for awhile, and decided this would be the right target platform. You can experiment with a real FPGA without breaking the bank.

In reality, you can learn a lot about FPGAs without ever using real hardware. As you’ll see, a lot of FPGA development occurs with simulated FPGAs that run on your PC. But if you are like me, blinking a virtual LED just isn’t as exciting as making a real one glow. However, for the first two examples I cover you don’t need any hardware beyond your computer. If you want to get ready, you can order an iCEstick and maybe it’ll arrive before Part III of this series if published.

Continue reading “Learning Verilog For FPGAs: The Tools And Building An Adder”