Within the messy world of international politics, a major consideration by governments concerns which types of kn0w-how and technology can be transferred and sold to other nations, with each type facing restrictions depending on how friendly the political relations are with the target country at that point in time. Amidst all of this, there are signs that a so far relatively minor player in the world of CPU instruction set architectures – RISC-V – may become a victim of this, as a bipartisan group of US politicians is petitioning the White House to restrict transfer of know-how (so-called Intellectual Property, or IP) to RISC-V, as this may benefit adversaries like China.

As a US citizen who is involved in the RISC-V ecosystem, [Andrew ‘bunnie’ Huang] feels rather strongly about this, and has written an open letter to the US President, pleading to not restrict the way that US citizens can deal with the Switzerland-based RISC-V organization. This comes as the California-based RISC-V startup SiFive has announced that it’ll lay off 20% of its workforce. Depending on how a restriction on RISC-V is implemented, this could mean that US citizens would be forbidden from contributing to this ISA and surrounding ecosystem.

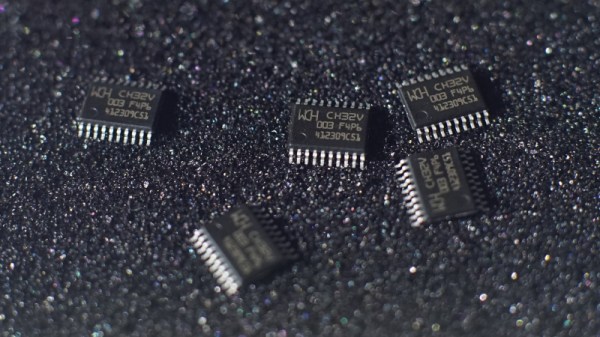

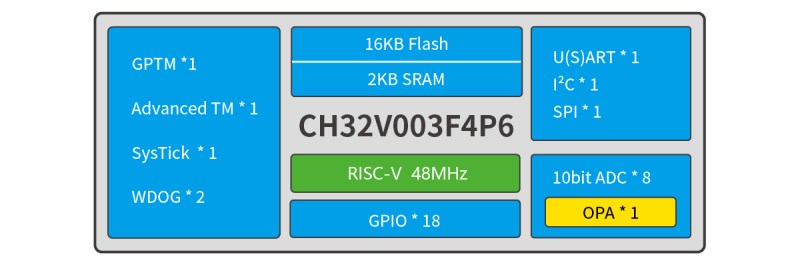

China has made it clear that RISC-V is a big part of its strategy to loosen its dependence on the West along with its investments in its MIPS-based Loongson processors, all of which strengthens the case for restricting US participation in RISC-V, even if it forces US companies like SiFive to move countries or cease its operations.

(Thanks to [cbjamo] for the tip)