There’s an understandably high level of interest in RISC-V processors among our community, but while we’ve devoured the various microcontroller offerings containing the open-source core it’s fair to say we’re still waiting on the promise of more capable hardware for anything like an affordable price. This could however change, as the last week or so has seen a flurry of interest surrounding SiFive, the fabless semiconductor company that has pioneered RISC-V technology. Amid speculation of a $2 billion buyout offer from the chip giant Intel it has been revealed that the company best known for the x86 line of processors has licensed the SiFive portfolio for its 7nm process. This includes their latest and fastest P550 64-bit core, bringing forward the prospect of readily available high-power RISC-V computing. Your GNU/Linux box could soon have a processor implementing an open-source ISA, without compromising too much on speed and, we hope, price.

All this sounds pretty rosy, but there is of course a downer for open-source hardware enthusiasts. These chips may rely on some open-source technologies, but sadly they will not themselves be open-source chips as there will be plenty of proprietary IP contained within them. We can thus only hope that Intel see fit to provide the same level of Linux support for them as they do for their x86 ranges, and we’re not left in the same situation with respect to ongoing support as we are with so many other chips. Meanwhile it’s worth remembering that SiFive are not the only player in the world of RISC-V cores, so it’s likely that competitors to the P550 and its stablemates will not be far behind.

If you’d like a more in-depth explanation of the true open-source nature of a RISC-V chip, we’ve featured something on that theme before.

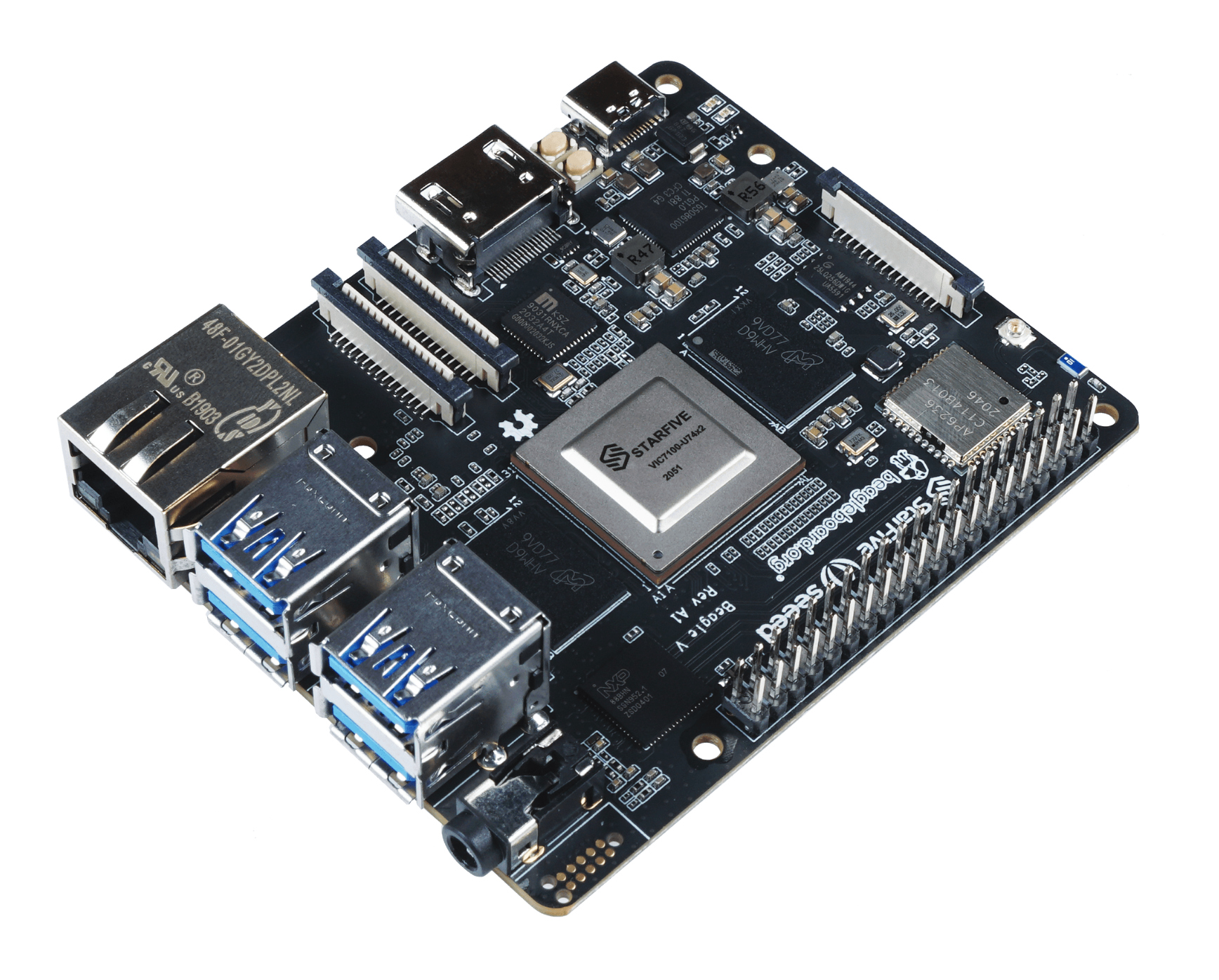

Header image: Gareth Halfacree, CC BY-SA 2.0.