Modern digital computers have complex instruction sets that runs on state-of-the-art ALUs which in turn are a consequence of miniaturized logic gates that are built with tiny transistors. These tiny transistors are essentially switches. You could imagine replacing with electromagnetic relays, and get what is called a relay computer. If you can imagine it, someone’s done it. In this case, [jhallenworld].

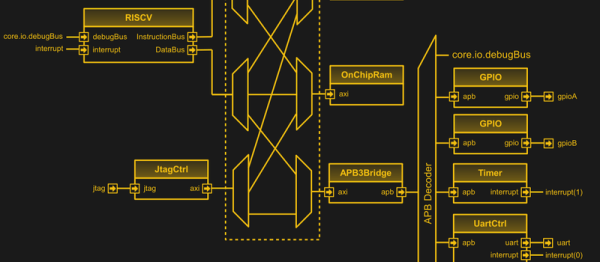

The Z3 was the first working programmable, fully automatic digital computer designed by Konrad Zuse. The board employs modern semiconductor devices such as memory and microcontrollers, however, the CPU is all relays. A hexadecimal keyboard allows for program entry and a segment display allows tracking the address and data. The program is piped into serial to the parallel decoder and fed to the CPU where the magic happens. Since the core is electromechanical it is possible to connect the output to peripherals such as a bell as demonstrated near the end of the video.

This project is a good balance of retro and modern to be useful to anyone interested in mechanical computers and should be a lot of fun for the geek kind. Hacking this computer to modify the instruction set should be equally rewarding and a good exercise for students of computing theory.

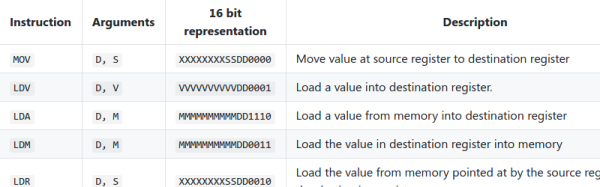

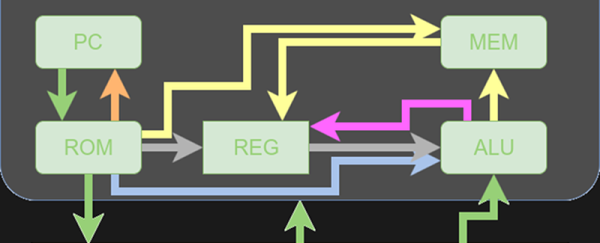

There is a SourceForge page dedicated to the project with the details on the project including the instruction set and architecture. Check out the video below and if you are inspired by the project, be sure to check out the [Clickity Clack]’a Videos on designing a relay computer bit by bit.