Intel, CPU manufacturer we all know and love, will buy Altera, makers of fine FPGAs, for $16.7 Billion.

While most of the news about this deal focuses on the future of FPGAs in the datacenter, getting Altera IP into Intel fab houses is equally interesting. Intel is the current king of putting transistors on a piece of silicon, and Intel’s ability to put a massive amount of transistors on a chip means FPGAs will become even more capable – more gates, more blocks, and more memory. The most capable Altera FPGAs are being made with a 28nm process; Intel could theoretically double the number of gates with the 14nm process used on the new Broadwell CPUs. There is most likely someone at Xilinx tearing their hair out right now, chain-smoking next to a pot of coffee.

News of this buy out comes about a week after Avago bought Broadcom in the biggest semiconductor deal ever, and a few months after NXP and Freescale merged. Cash Rules Everything Around Semiconductors, it seems.

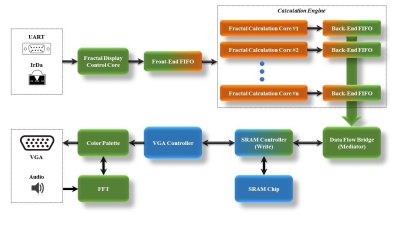

On the FPGA, a custom calculation engine, running at up to 150 MHz, does the math to generate the fractal. A Fast Fourier transform decomposes the audio input into frequencies, which are used to control the colors of the output image.

On the FPGA, a custom calculation engine, running at up to 150 MHz, does the math to generate the fractal. A Fast Fourier transform decomposes the audio input into frequencies, which are used to control the colors of the output image.