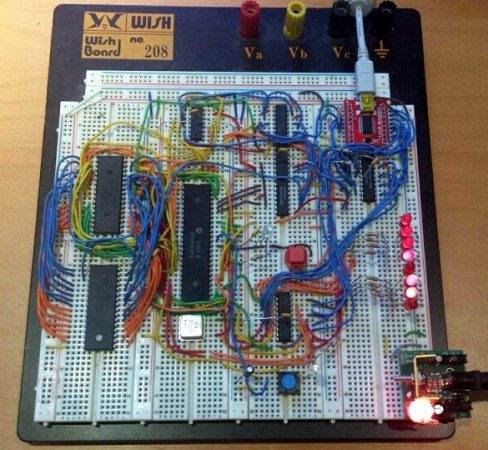

We’ve been lurking over at Big Mess ‘o Wires as [Steve] geared up for his 68000 computer build. One of his previous posts mentioned a working breadboard version but we figured it would be a ways off. Surprise, he’s got it working and what you see above took just 6 days of “occasional work” to get running.

The chip in use is actually a 68008 but we remember reading that he does plan to migrate to a 68000 because this one lacks the memory pins to address more than 1 MB of RAM. The trick here was just to get the thing running and he made some common choices to get there. For instance, he grounded the /DTACK in much the same way [Brian Benchoff] explained in his own 68k build.

We’re not sure if his address decoding was a time saver or not. If you study [Steve’s] original planning post you’ll learn that he’s going to use programmable logic to handle the address decoding. But above he wired up 74-series logic chips to perform these functions. On the one hand you know your Hardware Description Language isn’t the problem, but did you terminate one of those wires where you ought not?

Additional tripping points include a bouncing reset pin. Looking at that we’d tell [Steve] there’s a problem with his chip, except that this was his first thought as well. He went the extra mile by building and testing a replica of the reset system. This makes our brain spin… shouldn’t the reset be among the most reliable parts of a processor?

At any rate, great work so far. We can’t wait to see where this goes and we hope that it unfolds in a way that is as exciting as watching [Quinn Dunki’s] Veronica project take shape.