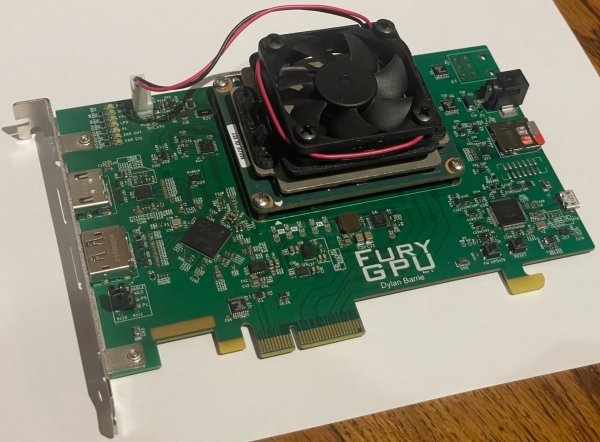

Today’s PCB design review is a board is from [Wificable]. iI’s a novel dual-SSD laptop adapter board! See, CPUs and chipsets often let you split wide PCIe links into multiple smaller width links. This board relies on a specific laptop with a specific CPU series, and a BIOS mod, to put two M.2 NVMe SSDs into a single SSD slot of a specific series’ laptop.

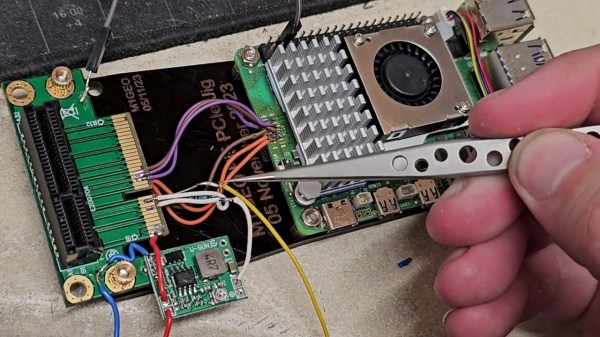

This board has two crucial factors – mechanical compatibility, and electrical function. Looking into mechanics, it’s a 0.8 mm thick PCB that plugs into a M.2 socket, and it has sockets for two SSDs on it – plenty of bending going on. For electronics, it has a PCIe REFCLK clock buffer, that [Wificable] found on Mouser – a must have for PCIe bifurcation, and a must-work for this board’s core! Apart from that, this is a 4-layer board, it basically has to be for diffpairs to work first-try.

Of course, the clock buffer chip is the main active component and the focus of the board, most likely mistakes will happen there – let’s look at the chip first.