We’re saddened to learn of the passing of Gershon Kingsley in December 2019 at the age of 97. The composer and electronic music pioneer was not exactly a household name, but the things he did with the Moog synthesizer, especially the surprise hit “Pop Corn”, which he wrote in 1969, are sure to be familiar. The song has been covered dozens of times, in the process of which the spelling of the name changed to “Popcorn.” We’re most familiar with the 1972 cover by Hot Butter, an earworm from our youth that doesn’t hide the Moog as deeply in the backing instruments as Kingsley did in the original. Or, perhaps you prefer the cover done by a robotic glockenspiel, because robotic glockenspiel.

A few months back, we covered the audacious plan to recover the radio gear from the Titanic. At the time, the potential salvors, Atlanta-based RMS Titanic, Inc., were seeking permission to cut into the submerged remains of the Titanic‘s Marconi room to remove as much of the wireless gear as possible. A federal judge granted permission for the salvage operation last Friday, giving the company the green light to prepare an expedition for this summer. The US government, through the National Oceanic and Atmospheric Administration and the National Park Service, argued strenuously to leave the wreck be and treat it as a tomb for the 1,527 victims. For our part, we had a great discussion about the merits in the comments section of the previous article. Now that it’s a done deal, we’d love to hear what you have to say about this again.

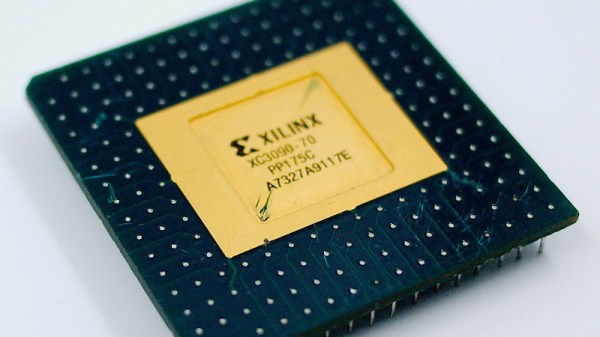

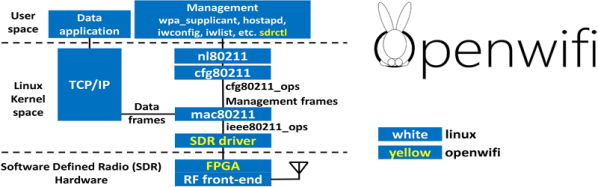

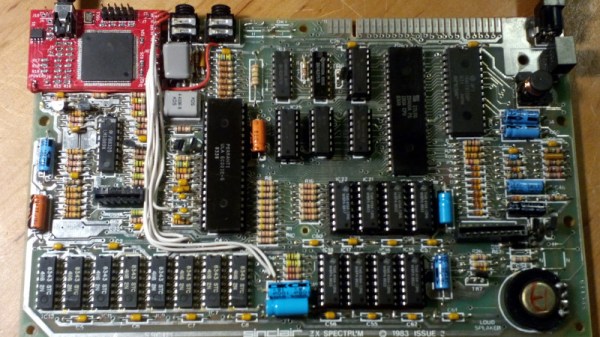

Although life appears to be slowly returning to what passes for normal, that doesn’t mean you might not still have some cycles to spare, especially when the time spent can bolster your skillset. And so if you’re looking to adding FPGAs to your resume, check out this remote lab on FPGA vision systems offered by Bonn-Rhein-Sieg University. The setup allows you to watch lectures, download code examples, and build them on your local computer, and then upload the resulting binaries to real hardware running on the lab’s servers in Germany. It sounds like a great way to get access to FPGA hardware that you’d otherwise have a hard time laying hands on. Or, you know, you could have just come to the 2019 Hackaday Superconference.

Speaking of skill-builders, oscilloscope owners who want to sharpen their skills could do worse than to listen to the advice of a real scope jockey like Allen Wolke. He recently posted a helpful video listing the five most common reasons for your scope giving “wrong” voltage readings. Spoiler alert: the instrument is probably doing exactly what you told it to do. As a scope newbie, we found the insights very helpful, and we can imagine even seasoned users could make simple mistakes like using the wrong probe attenuation or forgetting that scope response isn’t flat across its bandwidth.

Safety tip for the gearheads among us: your jack stands might be unsafe to use. Harbor Freight, the stalwart purveyor of cheap tools, has issued a recall of two different models of its jack stands. It seems that the pawls can kick out under the right conditions, sending the supported load crashing to the ground. This qualifies as a Very Bad Day for anyone unlucky enough to be working underneath when it happens. Defective jack stands can be returned to Harbor Freight for store credit, so check your garage and be safe out there in the shop.

And finally, because everyone loves a good flame war, Ars Technica has come up with a pronunciation guide for common tech terms. We have to admit that most of these are not surprising; few among the technology literate would mispronounce “Linux” or “sudo”. We will admit to a non-fanboy level of ignorance on whether the “X” in “iOS X” was a Roman numeral or not, but learning that the “iOS” part is correctly pronounced as three syllables, not two was a bit shocking. It’s all an exercise in pedantry that reminds us of a mildly heated discussion we had around the secret Hackaday writers’ bunker and whether “a LED” or “an LED” is the correct style. If the Internet was made for anything, it was stuff like this.