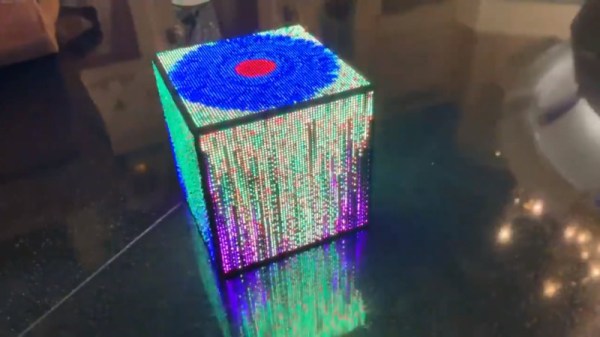

Like the tastes of the makers that build them, LED cubes come in all shapes and sizes. From the simplest 3x3x3 microcontroller test, to fancier bespoke installations, they’re a great way to learn a bunch of useful embedded techniques and show off at the same time. [kbob] has done exactly that in spades, with a glittering cube build of his own and published a repository with all the files.

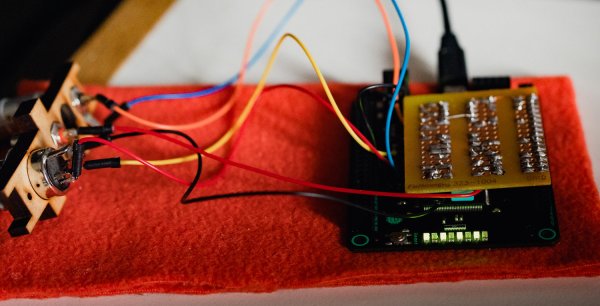

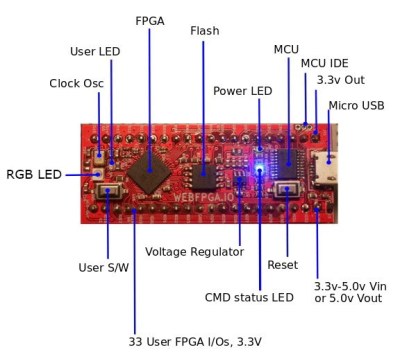

Just like a horde of orcs from Mordor, [kbob]’s cube is all about strength in numbers. Measuring 136 mm on each side, it’s constructed out of 64 x 64 P2 panels, packing 4096 LEDs per side, or 24,576 total. A Raspberry Pi is used to run the show, allowing a variety of animations to be run. Unfortunately, it lacks the raw horsepower to run this many LEDs at a decent frame rate. Instead, it’s teamed up with an ICEBreaker FPGA, which can churn out the required HUB75 signals for the panels without breaking a sweat.

Thanks to the high density of tiny LEDs, and the smooth framerate of the animations, the final effect is rather gorgeous. [kbob] notes that there’s actually a lot of people working on similar projects with ICEBreaker muscle; a recent video from [Piotr] is particularly impressive.

The LED cube will likely remain a staple for sometime, and we can’t wait to see what comes out next from the community. You can even throw in some OpenGL if you wanna get fancy. Video after the break.

Continue reading “This LED Cube Is One Heck Of An ICEBreaker”