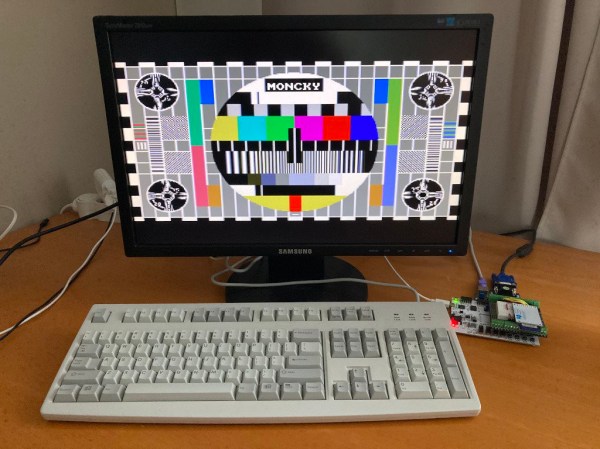

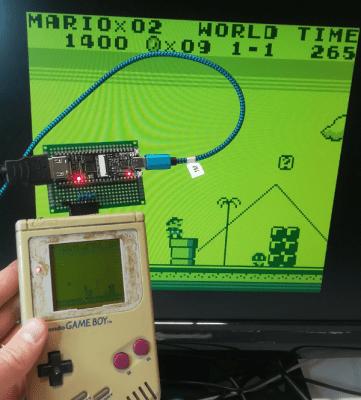

The classic Game Boy remains a firm favorite in the realm of retrocomputing. Revolutionary as it was at the time, by today’s standards its display is rather primitive, with no backlight and a usable area measuring only 47 mm x 44 mm. [Martoni] figured out a way to solve this, by developing GbVGA and GbHdmi, two projects that enable the Game Boy to connect to an external monitor. This way, you can play Super Mario Land without straining your eyes, and we can also image potential uses for those who stream their gameplay online.

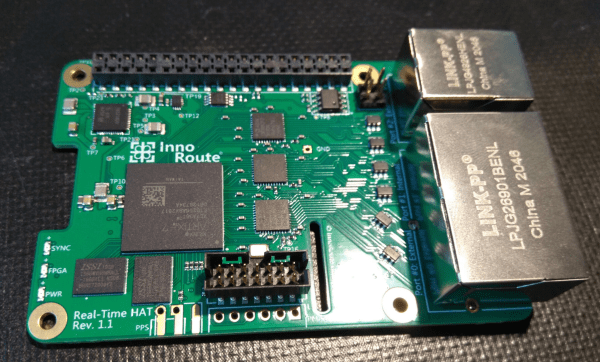

Getting the image data out of the Game Boy is surprisingly straightforward, and has been done a few times before. Basically, the connection between the CPU and the LCD screen is a serial interface with a 4 MHz clock, two data lines and two sync lines. [Martoni] uses pin headers sticking out of the Game Boy’s plastic case to connect these to a small FPGA board. The board in question is a Fireant for the VGA version and a Tang Nano 4K for the HMDI model. In either case the FPGA reads out each frame from the Game Boy’s LCD interface and draws the extracted image onto the monitor, using the same four shades of green as used on the original screen.

Getting the image data out of the Game Boy is surprisingly straightforward, and has been done a few times before. Basically, the connection between the CPU and the LCD screen is a serial interface with a 4 MHz clock, two data lines and two sync lines. [Martoni] uses pin headers sticking out of the Game Boy’s plastic case to connect these to a small FPGA board. The board in question is a Fireant for the VGA version and a Tang Nano 4K for the HMDI model. In either case the FPGA reads out each frame from the Game Boy’s LCD interface and draws the extracted image onto the monitor, using the same four shades of green as used on the original screen.

[Martoni] states that the ultimate goal of these projects is to make a Switch-like docking station for the original Game Boy, which is definitely something we’re looking forward to. Although adding external monitors to the Game Boy is not entirely new, we like the simplicity of this implementation and the fact that anyone can improve upon it thanks to the full source code being available. Similar hacks have been performed on the newer Game Boy Pocket and Game Boy Advance as well.