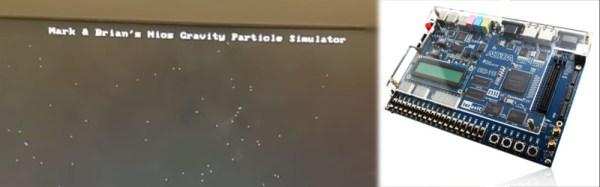

Death Stars were destroyed twice in the Star Wars movies and yet one still lives on in this 168 LED persistence of vision globe made by an MEng group at the University of Leeds in the UK. While Death Stars are in high demand, they mounted it on an axis tilted 23.4° (the same as the Earth) so that they can show the Earth overlaid with weather information, the ISS position, or a world clock.

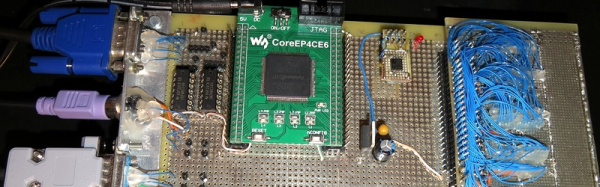

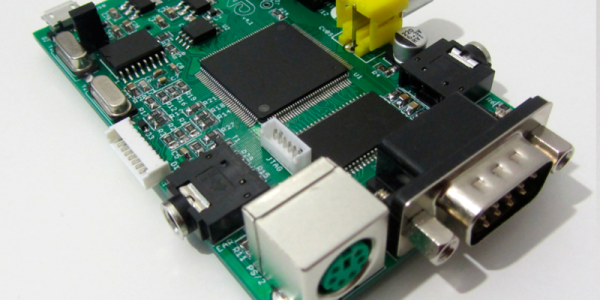

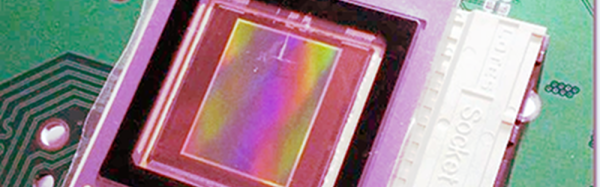

More details are available on their system overview page but briefly: rotating inside and mounted on the axis is a Raspberry Pi sending either video or still images through its HDMI port to a custom made FPGA-based HDMI decoder board. That board then controls 14 LED driver boards mounted on a well-balanced aluminum ring. All that requires 75W which is passed through a four-phase commutator. Rotation speed is 300 RPM with a frame rate of 10 FPS and as you can see in the videos below, it works quite well.