A fixture on many British high streets are pound shops. You may have an equivalent wherever in the world you are reading this; shops in which everything on sale has the same low price. They may be called dollar stores, one-Euro stores, or similar. In this case a pound, wich translates today to a shade under $1.24.

Amid the slightly random selection of groceries and household products are a small range of electronic goods. FM radios, USB cables and hubs, headphones, and mobile phone accessories. It was one of these that caught [Julian Ilett]’s eye, a USB power bank. (Video embedded below.)

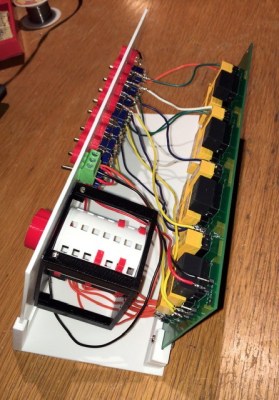

You don’t get much for a quid, and it shows in this product. A USB cable that gets warm at the slightest current, a claimed 800 mA of output at 5V from a claimed 1200 mAh capacity, and all from an 18650 Li-ion cell of indeterminate origin. The active component is an FM9833E SOIC-8 switching regulator and charger (220K PDF data sheet, in Chinese).

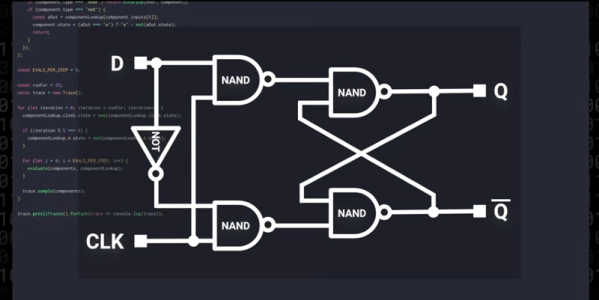

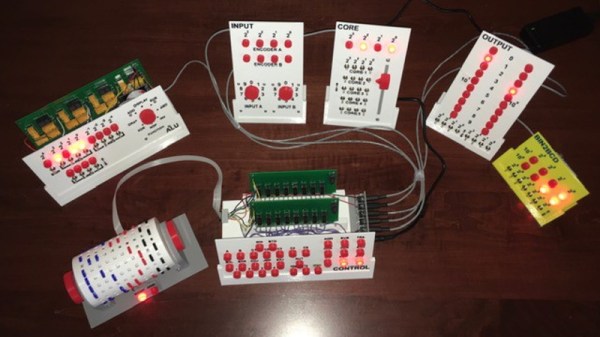

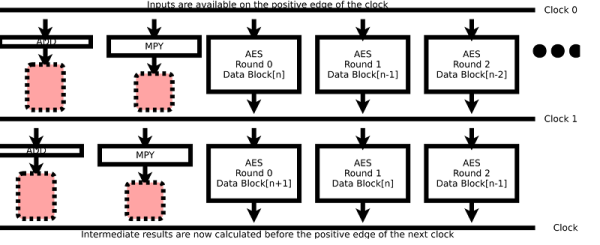

A straightforward teardown of a piece of near-junk consumer electronics would not normally be seen as something we’d tempt you with, but [Julian] goes on to have some rather pointless but entertaining fun with these devices. If you daisy-chain them, they can be shown to have the properties of rudimentary digital logic, and in the video we’ve put below the break it is this that he proceeds to demonstrate. We see a bistable latch, a set-reset latch, a very slow astable multivibrator, and finally he pulls out a load more power banks for a ring oscillator.

If only [MacGyver] had found himself trapped in a container of power banks somewhere from which only solving a complex mathematical conundrum could release him, perhaps he could have fashioned an entire computer! The best conclusion is the one given at the end of the video by [Julian] himself, in which he suggests (and we’re paraphrasing here) that if you feel the idea to be unworthy of merit, you can tell him so in the comments.

Continue reading “Cheap Powerbank Logic And Teardown” →