VR is in vogue, but getting on board requires a steep upfront cost. Hackaday.io user [Colin Pate] felt that $800 was a bit much for even the cheapest commercial 360-degree 3D camera, so he thought: ‘why not make my own for half that price?’

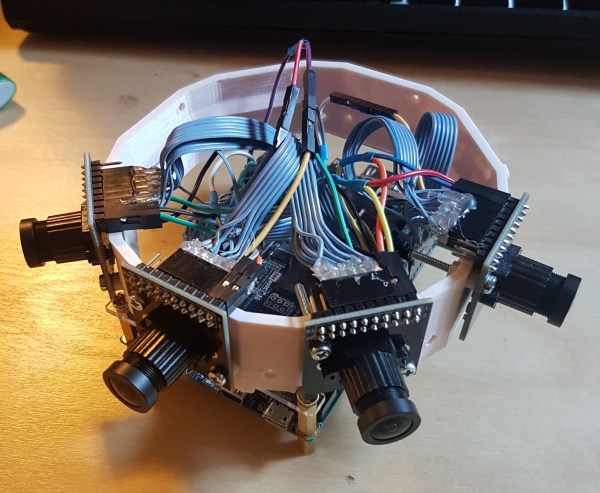

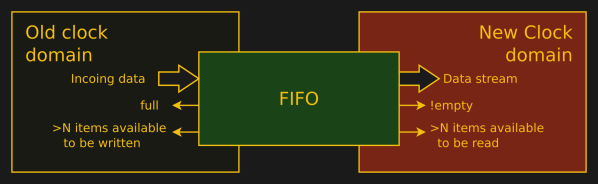

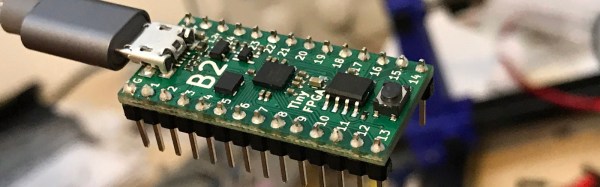

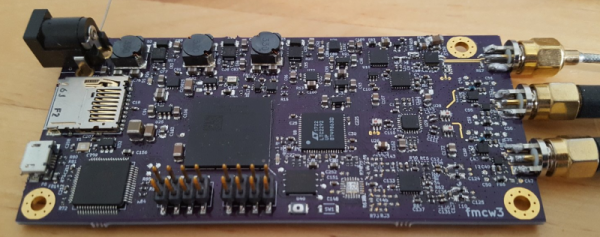

[Pate] knew he’d need a lot of bandwidth and many GPIO ports for the camera array, so he searched out the Altera Cyclone V SOC FPGA and a Terasic DE10-Nano development board to host it. At present, he has four Uctronics OV5642 cameras on his rig, chosen for their extensive documentation and support. The camera mount itself is a 3D-printed octagon so eight of the OC5642 can capture a full 360-degree photo.

Next: producing an image!

Continue reading “Immersive VR With A 200-Degree Stereoscopic Camera”