In a wonderful ode to tech nostalgia, The Taylor and Amy Show, comprised of YouTubers [Taylor] and [Amy], have released a new video “THE 6502 SONG”. This song had me singing along in roughly six clock cycles, possibly a little dancing around may have occurred as well. This isn’t just any chip they’re singing about; it’s the venerable 6502 microprocessor, the silicon heart behind iconic machines like the Apple II, Commodore 64/128, and the Atari 2600.

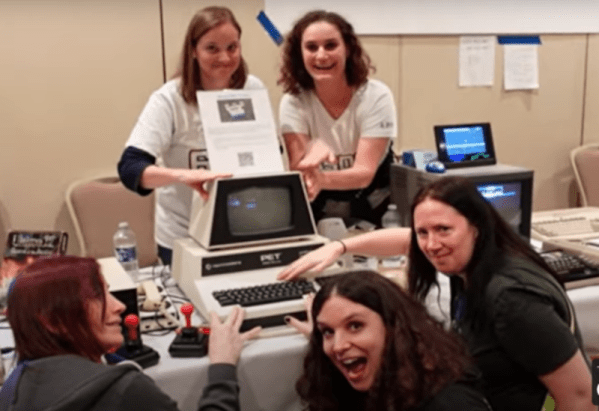

Their lyrics reminds me of when I lived for assembly language mnemonics and counting clock cycles, the “feeling” of a processor coming out of tristate to pronounce what it had learned in the last 500ns, and the undulations of the DRAMs like speed bumps. To top it off, portions of the song were actually recorded live at the Vintage Computer Festival Midwest 2023, where fans and computing history aficionados alike were treated to an impressive display of vintage tech.

What sets “THE 6502 SONG” apart isn’t just its catchy, melodic tune; it’s the expert blend of historical detail and genuine enthusiasm that resonates with everyone from grizzled assembly-language programmers to youngsters newly fascinated by the allure of 8-bit computing. With guest appearances from other female tech YouTubers like [Veronica Explains] and [Evie’s Revue], [AJ], [Jeri and Amy- Tilt5] and [FuzzyBad].

I believe [Chuck Peddle] father of the 6502, would be proud to see his creation live on and be appreciated so.

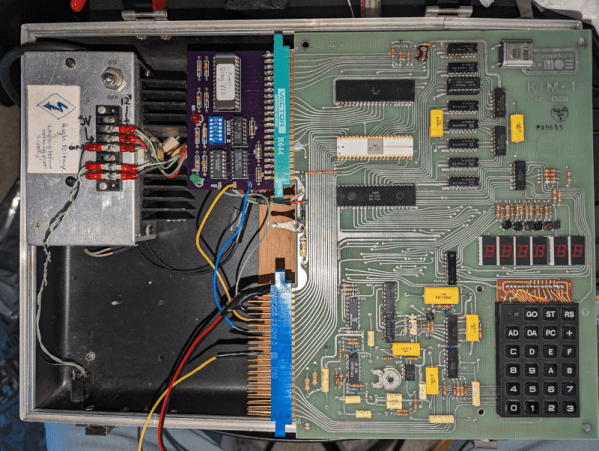

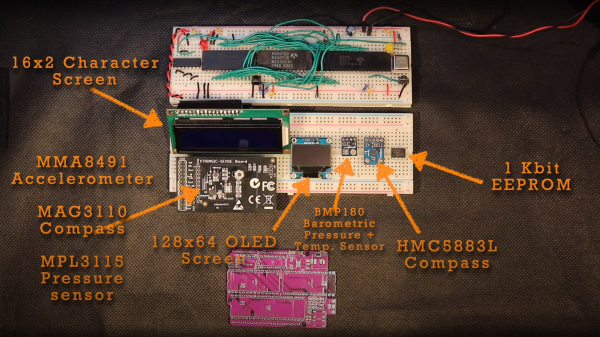

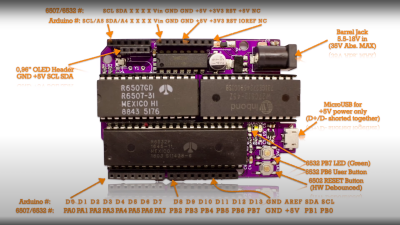

, setting a bit is simply a logical-OR operation, and resetting a bit is a simple logical-AND operation using the inversion (or one’s complement) bit to reset to form a bitmask. As many will already know, this process is necessary to code for a read or a write I2C operation. A further detail is that I2C uses an open-collector connection scheme, which means that no device on the bus may drive the bus to logical high; instead, they must release the drive by going to the high impedance state, and an external pull-up resistor will pull the bus high. The 6532 RIOT chip (used for I/O on the 65unio) does not have tristate control but instead uses a data direction register (DDR) to allow a pin to be an input. This will do the job just fine, albeit with slightly odd-looking code, until you know what’s going on.

, setting a bit is simply a logical-OR operation, and resetting a bit is a simple logical-AND operation using the inversion (or one’s complement) bit to reset to form a bitmask. As many will already know, this process is necessary to code for a read or a write I2C operation. A further detail is that I2C uses an open-collector connection scheme, which means that no device on the bus may drive the bus to logical high; instead, they must release the drive by going to the high impedance state, and an external pull-up resistor will pull the bus high. The 6532 RIOT chip (used for I/O on the 65unio) does not have tristate control but instead uses a data direction register (DDR) to allow a pin to be an input. This will do the job just fine, albeit with slightly odd-looking code, until you know what’s going on.