The first scramjet, an airbreathing jet engine capable of pushing an aircraft beyond Mach 5, was successfully flown in the early 1990s. But while pretty much any other technology you could imagine has progressed by leaps and bounds in the nearly 30 years that have passed, the state-of-the-art in hypersonic scramjets hasn’t moved much. We still don’t have practical hypersonic aircraft, military or otherwise, and any missiles that travel at those sort of speeds are rocket powered.

This is somewhat surprising since, at least on paper, the operating principle of the scramjet is simplicity itself. Air rushing into the engine is compressed by the geometry of the inlet, fuel is added, the mixture is ignited, and the resulting flow of expanded gases leaves the engine faster than it entered. There aren’t even any moving parts inside of a scramjet, it’s little more than a carefully shaped tube with fuel injectors and ignitors in it.

Unfortunately, pulling it off in practice is quite a bit harder. Part of the problem is that a scramjet doesn’t actually start working until the air entering the engine’s inlet is moving at around Mach 4, which makes testing them difficult and expensive. It’s possible to do it in a specially designed wind tunnel, but practically speaking, it ends up being easier to mount the engine to the front of a conventional rocket and get it up to speed that way. The downside is that such flights are one-way tickets, and end with the test article crashing into the ocean once it runs out of fuel.

But the bigger problem is that the core concept is deceptively simple. It’s easy to say you’ll just squirt some jet fuel into the stream of compressed air and light it up, but when that air is moving at thousands of miles per hour, keeping it burning is no small feat. Because of this, the operation of a scramjet has often been likened to trying to light a match in a hurricane; the challenge isn’t in the task, but in the environment you’re trying to perform it in.

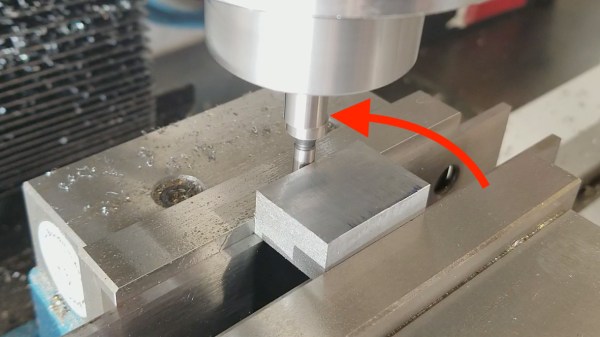

Now, both Aerojet Rocketdyne and Northrop Grumman think they may have found the solution: additive manufacturing. By 3D printing their scramjet engines, they can not only iterate through design revisions faster, but produce them far cheaper than they’ve been able to in the past. Even more importantly, it enables complex internal engine geometries that would have been more difficult to produce via traditional manufacturing.

Continue reading “3D Printing May Be The Key To Practical Scramjets”