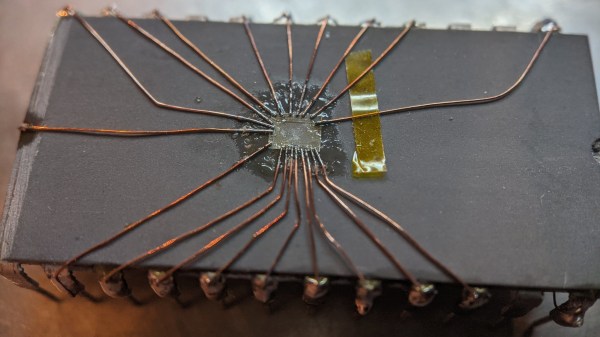

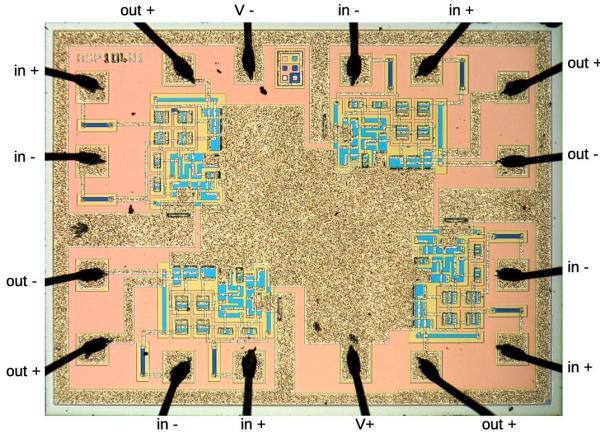

If you’ve ever fancied building a ZX Spectrum clone without hunting down ancient ULAs or soldering your way through 60+ chips, [Alex J. Lowry] has just dropped an exciting build. He has recreated the Leningrad-1, a Soviet-built Spectrum clone from 1988, with a refreshingly low component count: 44 off-the-shelf ICs, as he wrote us. That’s less than many modern clones like the Superfo Harlequin, yet without resorting to programmable logic. All schematics, Gerbers, and KiCad files are open-source, listed at the bottom of [Alex]’ build log.

The original Leningrad-1 was designed by Sergey Zonov during the late Soviet era, when cloning Western tech was less about piracy and more about survival. Zonov’s design nailed a sweet spot between affordability and usability, with enough compatibility to run 90-95% of Spectrum software. [Alex]’ replica preserves that spirit, with a few 21st-century tweaks for builders: silkscreened component values, clever PCB stacking with nylon standoffs, and a DIY-friendly mechanical keyboard hack using transparent keycaps.

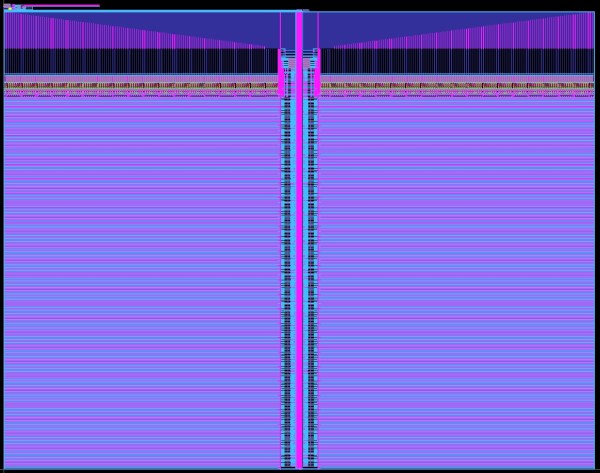

While Revision 0 still has some quirks – no SCART color output yet, occasional flickering borders with AY sound – [Alex] is planning for further improvements. Inspired to build your own? Read [Alex]’ full project log here.