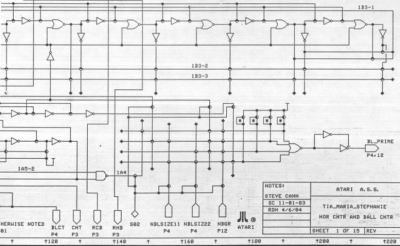

The most notable of the home computer and console hardware from the 8-bit golden era didn’t get their impressive sound and graphics from off-the-shelf silicon, instead they relied on secretive custom chipsets to get the edge over their competitors. Unfortunately for vintage gaming aficionados, those chips are now long out of production and in many cases there’s little information to be had about their operation.

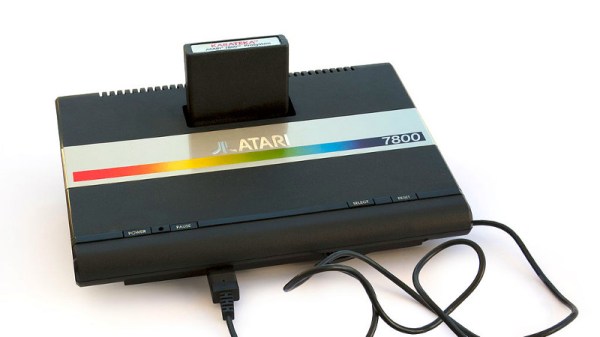

Which makes discovery of the schematics (PDF link) for the “Tia Maria” graphics chip found in the Atari 7800 console an unusual occurrence, and one which should be of special interest to the emulation community. They can be found alongside the rest of the Atari Museum’s 7800 information.

Which makes discovery of the schematics (PDF link) for the “Tia Maria” graphics chip found in the Atari 7800 console an unusual occurrence, and one which should be of special interest to the emulation community. They can be found alongside the rest of the Atari Museum’s 7800 information.

That such a useful document is available at all is due to a lucky find in a dumpster following the demise of Atari, when a treasure trove of documents was discarded. It seems that the existence of these schematics has been known within the Atari community for some time, and we expect before long this information will find its way into FPGA implementations of the 7800; especially since the system features nearly complete backwards compatibility with the massively successful Atari 2600.

When that happens we hope we’ll be able to bring it to you, but it’s not the first time someone’s made an Atari on an FPGA.

Via RetroRGB

Header image: Bilby [CC BY 3.0]